# **METRIC/SI**

# NASA TECHNICAL HANDBOOK

**National Aeronautics and Space Administration**

NASA-HDBK-4008 w/CHANGE 2: REVALIDATED w/ ADMINISTRATIVE/ EDITORIAL CHANGES 2025-06-18

Approved: 2013-12-02

# PROGRAMMABLE LOGIC DEVICES (PLD) HANDBOOK

# **DOCUMENT HISTORY LOG**

| Status       | Document | Change | <b>Approval Date</b> | Description                                                                                                                                                                                                                                |

|--------------|----------|--------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | Revision | Number |                      |                                                                                                                                                                                                                                            |

| Baseline     |          |        | 2013-12-02           | Initial Release                                                                                                                                                                                                                            |

| Baseline     |          | 1      | 2016-01-19           | Revalidated w/Administrative/Editorial<br>Changes—This NASA Technical<br>Handbook was reviewed, and no technical<br>changes resulted. Administrative changes<br>to conform to the current template and<br>editorial corrections were made. |

| Revalidation |          | 2      | 2025-06-18           | Revalidated -This NASA Technical<br>Handbook was reviewed, and no technical<br>changes resulted.                                                                                                                                           |

#### **FOREWORD**

This NASA Technical Standard is published by the National Aeronautics and Space Administration (NASA) to provide uniform engineering and technical requirements for processes, procedures, practices, and methods that have been endorsed as standard for NASA programs and projects, including requirements for selection, application, and design criteria of an item.

This NASA Technical Standard is approved for use by NASA Headquarters and NASA Centers and Facilities and may be cited in contract, program, and other Agency documents as a technical requirement. It may also apply to the Jet Propulsion Laboratory and other contractors only to the extent specified or referenced in applicable contracts.

This NASA Technical Handbook establishes programmable logic design engineering guidance. It originated from multiple requests for additional guidance, rationale, resources, references and lessons learned for acquiring, managing, developing, assuring, and maintaining NASA systems.

Requests for information should be submitted via "Feedback" at <a href="https://standards.nasa.gov">https://standards.nasa.gov</a>.

| Original Signed By  | 12/2/2013     |

|---------------------|---------------|

| Ralph R. Roe, Jr.   | Approval Date |

| NASA Chief Engineer |               |

# **TABLE OF CONTENTS**

| SEC <sub>1</sub> | <u>'ION</u>                                             |

|------------------|---------------------------------------------------------|

| DOC              | UMENT HISTORY LOG                                       |

|                  | EWORD.                                                  |

|                  | LE OF CONTENTS                                          |

|                  | OF APPENDICES                                           |

|                  | OF FIGURES.                                             |

|                  | OF TABLES.                                              |

|                  |                                                         |

| 1.               | SCOPE                                                   |

| 1.1              | Purpose                                                 |

| 1.2              | Applicability                                           |

|                  |                                                         |

| 2.               | APPLICABLE DOCUMENTS                                    |

| 2.1              | General                                                 |

| 2.2              | Government Documents                                    |

| 2.3              | Non-Government Documents                                |

| 2.4              | Order of Precedence                                     |

| 2                | A CRONWAG AND DEFINITIONS                               |

| 3.               | ACRONYMS AND DEFINITIONS                                |

| 3.1              | Acronyms and Abbreviations                              |

| 3.2              | Definitions                                             |

| 4.               | LIFE CYCLE AND DEVICE DEVELOPMENT                       |

| 4.1              | Life Cycle Definitions                                  |

|                  |                                                         |

| <b>5.</b>        | PLANNING AND REQUIREMENTS PHASE                         |

| 5.1              | Roles and Responsibilities                              |

| 5.2              | The Development Plan                                    |

| 5.3              | Requirements                                            |

| 5.4              | Verification Plan                                       |

| 6.               | PRELIMINARY DESIGN PHASE                                |

| 6.1              | Entry Criteria                                          |

| 6.2              | Design Specification (Preliminary Version)              |

| 6.3              | Interface Definition (Preliminary Version)              |

| 6.4              | Use of Intellectual Property (In-House or Out-of-House) |

| 6.5              | Exit Criteria                                           |

| J.J              | 1-2217 V119V114                                         |

# **TABLE OF CONTENTS (Continued)**

| <u>SECTION</u> |                                                |   |  |

|----------------|------------------------------------------------|---|--|

| 7.             | DETAILED DESIGN PHASE                          | 3 |  |

| 7.1            | Entry Criteria                                 | 3 |  |

| 7.2            | Coding Standard                                | 3 |  |

| 7.3            | Design Standard/Best Practices                 | 3 |  |

| 7.4            | Design Specification                           | 4 |  |

| 7.5            | Board and PLD Interface Considerations         | 4 |  |

| 7.6            | Design Test Coverage                           | 4 |  |

| 7.7            | Software Development for an Embedded Processor | 4 |  |

| 7.8            | Exit Criteria                                  | 4 |  |

| 8.             | DESIGN IMPLEMENTATION PHASE                    | 4 |  |

| 8.1            | Entry Criteria                                 | 5 |  |

| 8.2            | Implementation                                 | 5 |  |

| 8.3            | Verification Preparation                       | 5 |  |

| 8.4            | Synthesis and Timing Analysis                  | 5 |  |

| 8.5            | Baseline Work Products                         | 5 |  |

| 8.6            | Generate the Programming File                  | 5 |  |

| 8.7            | Exit Criteria                                  | 5 |  |

| 9.             | VERIFICATION                                   | 6 |  |

| 9.1            | Entry Criteria                                 | 6 |  |

| 9.2            | Test Process                                   | 6 |  |

| 9.3            | Simulation                                     | 6 |  |

| 9.4            | Independent Peer Verification                  | 6 |  |

| 9.5            | Verification Review                            | 6 |  |

| 9.6            | Regression Testing                             | 6 |  |

| 9.7            | Hardware Verification                          | 6 |  |

| 9.8            | Exit Criteria                                  | 6 |  |

| 10.            | DELIVERY                                       | 6 |  |

| 10.1           | PLD Programming                                | 7 |  |

| 10.2           | PLD Marking                                    | 7 |  |

| 11.            | MAINTENANCE                                    | 7 |  |

| 11.1           | Design Libraries                               | 7 |  |

| 11.2           | Active Designs                                 | 7 |  |

| 11.3           | Post-Delivery Anomalies                        | 7 |  |

# **TABLE OF CONTENTS (Continued)**

| SECTIO                          | <u>ON</u>                                                                                                                                                                                                                                                                                                      | <b>PAGE</b>                                |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| 11.4                            | Retired Designs                                                                                                                                                                                                                                                                                                | 73                                         |

| 12.                             | RELEASE PROCESS                                                                                                                                                                                                                                                                                                | 73                                         |

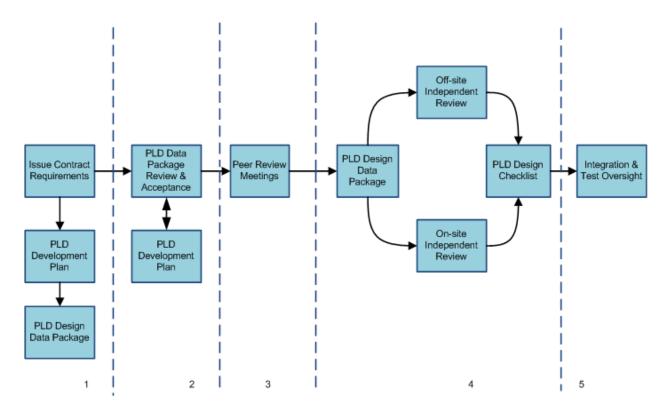

| <b>13.</b> 13.1 13.2            | OUT-OF-HOUSE CONSIDERATIONS  Contract Statement of Work (SOW)  The Flight PLD Design Review Process                                                                                                                                                                                                            | <b>74</b> 74 75                            |

|                                 | LIST OF APPENDICES                                                                                                                                                                                                                                                                                             |                                            |

| APPEN                           | <u>DIX</u>                                                                                                                                                                                                                                                                                                     | <b>PAGE</b>                                |

| A<br>B<br>C<br>D<br>E<br>F      | Suggested Source Code Header and Footer Template Sample Peer Review Checklists Customizing Life-Cycle Product Guidance Safety Critical Board Level Design Considerations Guidance                                                                                                                              | 79<br>81<br>98<br>102<br>103<br>105<br>118 |

|                                 | LIST OF FIGURES                                                                                                                                                                                                                                                                                                |                                            |

| <u>FIGURI</u>                   | <u> </u>                                                                                                                                                                                                                                                                                                       | <b>PAGE</b>                                |

| 1<br>2<br>3<br>4<br>5<br>6<br>7 | PLD Life-Cycle Development Phases  Example Development Team Role-Based Organization Chart  Sample Clock Tree Diagram  Flight Project PLD Design Review Process  Recommended Power-On Reset Implementation  Glitches Due to Input Slew Rate Violations  Sneak Path in Some LSTTL from Output to V <sub>CC</sub> | 15<br>20<br>48<br>75<br>106<br>110<br>112  |

# LIST OF TABLES

| <b>TABLE</b> |                                                         | <u>PAGE</u> |

|--------------|---------------------------------------------------------|-------------|

| 1            | List of Possible Reviews.                               | 27          |

| 2            | Sample Verification Matrix                              | 32          |

| 3            | Example of Two-Corner Analysis                          | 54          |

| 4            | Regression Testing                                      | 68          |

| 5            | PLD Classification.                                     | 98          |

| 6            | PLD Development Customization Recommendations           | 100         |

| 7            | Guidance for PLD Life Cycle Products at Various Reviews |             |

# PROGRAMMABLE LOGIC DEVICES (PLDs) HANDBOOK

### 1. SCOPE

This NASA Technical Handbook outlines a life cycle as a guideline for planning, designing, verifying and maintaining programmable logic devices (PLDs). Additionally, best practices are recommended for different PLD development phases. This NASA Technical Handbook provides guidance to perform project activities. It covers all aspects of the design cycle from initial planning through release and maintenance. The specific types of PLDs this NASA Technical Handbook addresses are as follows:

- Field-programmable gate array (FPGA).

- Complex programmable logic device (CPLD).

## 1.1 Purpose

The purpose of this NASA Technical Handbook is to establish PLD design engineering guidance.

The trend toward the increased use of PLDs in aerospace systems requires increased expertise in the design, development, and verification of these systems. Hardware designers are now expected to implement PLD designs that are as complex as traditional microprocessor-based systems that were designed in some cases by large teams of engineers.

The development of successful PLDs requires a coordinated effort. This NASA Technical Handbook contains guidelines that provide for a consistent approach based on best practices for the development of PLDs for flight and ground support systems across NASA Centers. The advancing technology in PLDs has allowed for the implementation of more complex designs in single devices. Many of these devices designed within NASA systems perform critical operations. The guidelines in this NASA Technical Handbook serve to increase confidence in the quality of PLD designs.

### 1.2 Applicability

This NASA Technical Handbook provides engineering guidance applicable to programmable logic design. It serves as a primer for sound engineering design practice and can be used in its entirety, or in portions thereof, in conjunction with other available design resources.

This NASA Technical Handbook is approved for use by NASA Headquarters and NASA Centers and Facilities. It may also apply to the Jet Propulsion Laboratory or other contractors only to the extent specified or referenced in their contracts.

This NASA Technical Handbook, or portions thereof, may be referenced in contract, program, and other Agency documents for guidance. When it contains procedural or process requirements, they may be cited in contract, program, and other Agency documents.

#### 2. APPLICABLE DOCUMENTS

#### 2.1 General

The documents listed in this section are applicable to the guidance in this NASA Technical Handbook.

- **2.1.1** The latest issuances of cited documents shall apply unless specific versions are designated.

- **2.1.2** Non-use of specifically designated versions shall be approved by the responsible Technical Authority.

The applicable documents are accessible at <a href="https://standards.nasa.gov">https://standards.nasa.gov</a> or may be obtained directly from the Standards Developing Body or other document distributors. Additional documents and design resources are available at <a href="https://nen.nasa.gov/web/pld">https://nen.nasa.gov/web/pld</a>.

#### 2.2 Government Documents

#### **National Aeronautics and Space Administration (NASA)**

NASA-HDBK-8739.23 NASA Complex Electronics Handbook for Assurance

Professional

NPR 7123.1 NASA Systems Engineering Processes and Requirements

NPR 8715.3C NASA General Safety Program Requirements

#### 2.3 Non-Government Documents

None.

### 2.4 Order of Precedence

This NASA Technical Handbook provides guidance for planning, designing, verifying and maintaining programmable logic devices but does not supersede or waive established Agency requirements/guidance found in other documentation.

### 3. ACRONYMS AND DEFINITIONS

### 3.1 Acronyms and Abbreviations

A/D analog to digital AID altered item drawing

ASIC application specific integrated circuit

CDC clock domain crossing CDR critical design review

CLK clock

CLKA/B clock A or B CLKBUF clock buffer

CM configuration management

CMOS complementary metal oxide semiconductor

COTS commercial off the shelf

CPLD complex programmable logic device

CPU central processing unit

CRC cyclic redundancy check

CVS Concurrent Versions System

CxP Constellation Program

DC direct current

DDP detailed design phase

DDR double data rate

DFF d-flip-flop

DLL delay-locked loop

DOORS Dynamic Object-Oriented Requirements System

EDAC error detection and correction

EEPROM electrically erasable programmable read-only memory

EIDP end item data package EMI electromagnetic interference

ESD electrostatic discharge

ETU engineering test unit

FET field effect transistor

FIFO first in, first out

FPGA field-programmable gate array

FSM finite state machine

GIDEP Government Industry Data Exchange Program

GPU graphics processing unit

HALE high altitude long endurance

HCLK hardwired CLK driver

HCLKBUF buffer for HCLK

HDL hardware description language HSI hardware/software integration

I/O input/output

IC integrated circuit

IP intellectual property

ITAR International Traffic in Arms Regulations

JTAG Joint Test Action Group

LSTTL Low-power Schottky Transistor Transistor Logic

LVDS low voltage differential signaling

ms millisecond N/C no connect

NASA National Aeronautics and Space Administration

ns nanosecond OTS off-the-shelf

PCB printed circuit board

PCI peripheral component interconnect

PDP preliminary design phase PDR preliminary design review PLD programmable logic device

PLL phase-locked loop PnR place and route POC point of contact POR power-on reset

PROM programmable read-only memory PRP planning and requirements phase

QA quality assurance

RDD revision description document

ROM read-only memory

RTL register-transfer level

SDF Standard Delay Format

SERDES serializer-deserializer

SET single event transient

SEU single event upset

SMA Safety and Mission Assurance

SOW statement of work

SRAM static random access memory SSO simultaneously switching output

STA static timing analysis

SVN Subversion

TBD to be determined

TID total ionizing dose

TMR triple modular redundancy

TRST test reset (JTAG test reset signal)

TTL transistor-transistor logic

UART universal asynchronous receiver/transmitter

VDD Version Description Document

VHDL very high speed integrated circuit (VHSIC) hardware

description language (HDL)

VHSIC very high speed integrated circuit

VIO voltage input/output VP verification phase

#### 3.2 Definitions

Asynchronous: Inputs and/or logic that changes independently of clock changes.

<u>Board</u>: Describes the electronic assembly that contains the PLD. *Note: The board can be purchased or customized for the design.*

<u>Brownout</u>: A condition where the voltage of the power source drops below the nominal operating range because of an excessive current loading.

<u>CLKBUF</u>: A clock buffer type in a MicroSemi FPGA.

<u>Clock Domain</u>: A clock domain is a block of circuitry that operates at a single clock frequency that may differ from the frequency of other blocks on the same chip. A clock domain crossing occurs whenever data is transferred from a flop driven by one clock to a flop driven by another clock.

Cold spare/ing: A spare redundant unit that remains unpowered when inactive. *Note:* A cold sparing device is designed to allow powered input signals to be applied to the unpowered device without damage to the device.

<u>Crosstalk</u>: Any phenomenon by which a signal transmitted on one circuit or channel of a transmission system creates an undesired effect in another circuit or channel. *Note: Undesired capacitive, inductive, or conductive coupling from one circuit, part of a circuit, or channel to another is what usually causes crosstalk.*

<u>Delivering Organization</u>: The organization that is responsible for developing and delivering the PLD design.

<u>Fault Injection</u>: A technique for improving the coverage of a test by introducing faults to test code paths.

<u>Gray Code</u>: An encoding of numbers so that adjacent numbers have a single digit differing by 1.

<u>Hamming Code</u>: A linear code devised for detecting and correcting errors in digital data.

**HCLK**: A clock buffer type in a MicroSemi FPGA.

<u>HCLKBUF</u>: A clock buffer type in a MicroSemi FPGA.

<u>Hystereis</u>: A phenomenon wherein two (or more) physical quantities bear a relationship that depends on prior history. More specifically, the response Y takes on different values for an increasing input X than for a decreasing X.

Krad (Si): 1000 rad (Si), see also rad (Si).

Metastability: The ability of a digital electronic system to persist for an unbounded time in an unstable equilibrium or metastable state. In metastable states, the circuit may be unable to settle into a stable '0' or '1' logic level within the time required for proper circuit operation. As a result, the circuit can act in unpredictable ways, and may lead to a system failure.

<u>Primitives</u>: The physical hardware components that exist in the PLD. These primitives will be connected together in a specific way on your PLD in order to fulfill your design as specified. For FPGAs, the most basic primitives are flip-flops and lookup tables.

Rad (Si): The quantity of any type of ionizing radiation that will impart 100 ergs of energy per gram of silicon.

$\underline{\mathbf{R}}_{\text{term:}}$  Value of the termination resistor.

<u>Synthesis</u>: A process that starts from a high level of logic abstraction (typically Verilog or Very High Speed Integrated Circuit (VHSIC) Hardware Description Language (VHDL)) and automatically creates a lower level of logic abstraction using a library containing primitives.

Test Bench: To simulate a design, the designer needs both the design under test or unit under test and the stimulus provided by the test bench. *Note: A test bench is a Hardware Description Language (HDL) code that allows the designer to provide a documented, repeatable set of stimuli that is portable across different simulators. A test bench can be as simple as a file with clock and input data or a more complicated file that includes error checking, file input and output, and conditional testing. Verilog designers sometimes refer to a Verilog test fixture. "Test bench" and "test fixture" are used synonymously throughout this NASA Technical Handbook.*

<u>Test Procedure</u>: A document that delineates the test steps required to verify full compliance of the PLD implementation with the requirements.

Tool: Describes the PLD software design package used to generate the PLD design.

T<sub>PD</sub>: Refers to the propagation delay time of a device.

T<sub>REM:</sub> Refers to the synchronous clear preset or removal time.

$\underline{V}_{CC}$ : Refers to the power supply pin for a bipolar junction transistor integrated circuit (IC).

$\underline{V_{DD}}$ : Refers to the power supply pin for Complementary Metal Oxide Semiconductor (CMOS) ICs.

V<sub>IH:</sub> Refers to the voltage threshold for input high.

Verification: The determination that the end product meets all of the specified

requirements.

Z<sub>driver</sub>: Output impedance of the driving circuit.

$\underline{Z}_{trace}$ : Characteristic impedance of a circuit board trace.

#### 4. LIFE CYCLE AND DEVICE DEVELOPMENT

Life cycle development for the PLD development process consists of a series of phases with entry and exit criteria. This section describes this series of development phases and the products developed in each phase. Depending on the criticality and risk to the project, two or more phases can be combined into a single phase. Additionally, device development does not typically consist of a single pass through each phase. The phases iterate based on the needs of the design.

This section provides a typical template for the development life cycle. The remainder of this NASA Technical Handbook uses this development cycle for describing what products to complete in each section.

# 4.1 Life-Cycle Definitions

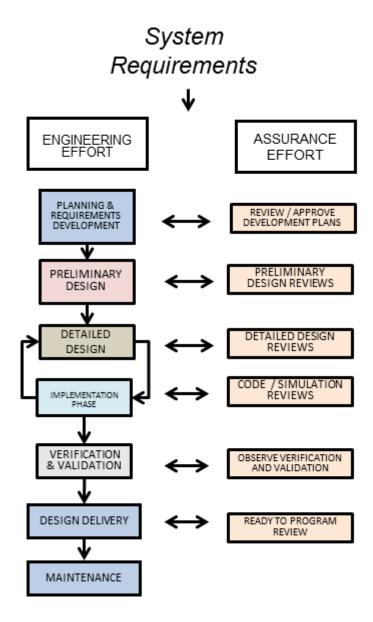

The sections that follow describe the PLD life-cycle phases. See also figure 1, PLD Life-Cycle Development Phases.

# 4.1.1 Planning and Requirements Phase

Development planning is essential for early identification of all the development needs and risks. It also provides the PLD design team with a clear view of the near- and long-term objectives and goals. The planning and requirements phase (PRP) occurs when requirements have been allocated to the board where the PLD resides. High-level system requirements flow down and the design team uses them to generate the PLD requirements.

The planning phase includes documenting a development plan that all developers follow. The plan documents the systematic approach used to manage, design, develop, verify, document, and review all PLDs delivered. The design team can customize the level of detail to the complexity of the design and project. Appendix C provides more details on customization.

During development of the PLD, the design team reviews the requirements and/or the development plan and updates it as required. Section 5 describes this phase in greater detail.

Figure 1—PLD Life-Cycle Development Phases

### 4.1.2 Preliminary Design Phase

During the preliminary design phase (PDP), the design team generates a top-level design based on the device requirements. This top-level design includes block diagrams and data flow diagrams that serve as the design architecture. Design trade studies are completed during this phase. This phase is complete when the stakeholders identified in the PRP approve the preliminary design. Section 6 describes this phase in greater detail.

## 4.1.3 Detailed Design Phase

The detailed design phase (DDP) begins after approval of the preliminary design. During the DDP, the preliminary design is used to generate a more detailed design based on the requirements and architecture. This phase iterates as needed with the design implementation phase to further modify and/or expand until it meets all requirements. This phase is complete when the stakeholders identified in the PRP approve the documented detailed design. Section 7 describes this phase in greater detail.

### 4.1.4 Design Implementation Phase

During the design implementation phase, design capture (such as coding in a hardware description language (HDL)) is completed. The design team performs design simulation, synthesis, place and route (PnR), and timing analyses. The design may be tested on a development board and/or hardware resembling the final flight system. This phase iterates with the DDP as needed. Section 8 describes this phase in greater detail.

#### **4.1.5** Verification Phase

Verification determines that the end product meets all of the specified requirements whereas validation determines the requirements are correct. Validation is beyond the scope of this document since it often requires a higher level of integration. Verification activities include reviews, tests, and simulations in accordance with the plan developed in the PRP. Formal acceptance of the final design occurs at the conclusion of the verification phase (VP). Section 9 describes this phase in greater detail.

#### 4.1.6 Delivery Phase

After successful verification, the design team releases the completed design for integration into the next higher-level assembly (e.g., board, box, etc.). Section 10 describes this phase in greater detail.

#### 4.1.7 Maintenance Phase

The development team continues to provide troubleshooting support for issues deemed unsolvable by the user of the design, and investigates and tracks potential design anomalies to completion. Maintenance support covers any issues reported after the delivery. Section 11 describes this phase in greater detail.

# 5. PLANNING AND REQUIREMENTS PHASE

Numerous projects do project planning as part of the system planning. All items that are identified in the PRP can be done separately or as part of the larger planning.

The output of the PRP for a PLD can include documents, such as:

- a. A development plan.

- b. A requirements document.

- c. A verification plan.

The design team applies customization to each of the documents depending on the project. Appendix C shows a proposed PLD classification to aid in determining an appropriate customization.

All planning and requirements documentation and development will need to be coordinated with Project Management, System Engineering, and the Chief Engineer. The use of NPR 7123.1, NASA Systems Engineering Processes and Requirements, continues to serve as the governing requirements for system development.

## 5.1 Roles and Responsibilities

The scope of work for each role on the development team varies with the size and complexity of the development. A development team member may perform multiple roles for a simple development. Conversely, multiple individuals might be required to share the responsibilities for a single role for a large development. Work with the line management to set the initial roles and responsibilities for the development effort. This can then be worked into the efforts defined by the project.

A PLD development effort typically includes the following roles and responsibilities:

- a. PLD Team Lead.

- (1) Co-develop the development plan with the technical development lead.

- (2) Manage the development plan.

- (3) Manage budget and schedule.

- (4) Collect development metrics and provide status to project management.

- (5) Manage procurement contracts.

- b. PLD Technical Development Lead.

- (1) Co-develop the development plan with the PLD team lead.

- (2) Provide single point of contact (POC) for technical interactions with external stakeholders.

- (3) Oversee the technical aspect of the overall development and the end delivery of the design (including design analyses/trade studies, identifying intellectual property (IP) core usage, etc.).

- (4) Develop, negotiate, and maintain the PLD design requirements.

- (5) Select design and configuration management (CM) tools when necessary.

- (6) Develop/select the revision control process and associated tools(s).

- (7) Owner of the PLD design specification.

- (8) Manage design tools (maintenance support, license files, tool availability).

- (9) Ensure adherence to the required design process.

- (10) Responsible for the overall quality and delivery of the end product.

- (11) Assign responsibilities to members of the development team.

- c. PLD Configuration Lead/Librarian.

- (1) Manage revision control.

- (2) Maintain the design repository/library.

- (3) Build and release (official and unofficial) design into the test venue and for delivery.

- (4) Assemble the end item data package (EIDP) of the official releases.

- d. Verification Lead.

- (1) Responsible for the development of the PLD verification plan, including defining test (hardware and software) requirements, verification items for simulation and pass/fail criteria for each verification item.

- (2) Support the test lead on the PLD hardware verification plan development and hardware testing.

- (3) Oversee and ensure the completion of the verification activities.

- (4) Archive the verification results.

- (5) Generate test reports.

- (6) Contribute to development of functional coverage checks.

- e. Design Engineer.

- (1) Design the assigned design modules.

- (2) Generate pertinent documentation for the assigned design modules.

- (3) Perform incremental testing.

- (4) Contribute to the development of functional coverage checks.

- f. Possible Customer/Stakeholders

- (1) Board Design Lead: Owner of the board where the PLD resides. The board design lead works with the technical development lead on defining the PLD requirements, ensures compatible interface between the board and PLD throughout the design phases, and coordinates the overall verification effort for the board.

- (2) Test Lead: Responsible for leading the effort on completing the PLD verification at the board level and providing a single POC for reporting the testing status to the PLD development team. The test lead is the source of the testability requirements (software, test points, fault injection, etc.).

- (3) Test Equipment Development Lead: Responsible for developing and negotiating the functional requirements for the test equipment with the technical development lead.

- (4) Safety and Mission Assurance (SMA) personnel: Serves as an independent assessor. NASA-HDBK-8739.23, NASA Complex Electronics Handbook for Assurance Professional, documents the SMA roles and responsibilities, and they are NOT duplicated in this document. In addition for safety-critical projects, SMA personnel will also use NPR 8715.3C, NASA General Safety Program Requirements, for applicability to PLDs.

- (5) System Safety Engineer.

- (6) Users: People who operate the PLD in its intended applications. Depending on the design, users may include:

- A. Software developers.

- B. Subsystem engineers.

- C. System engineers.

- D. Test engineers.

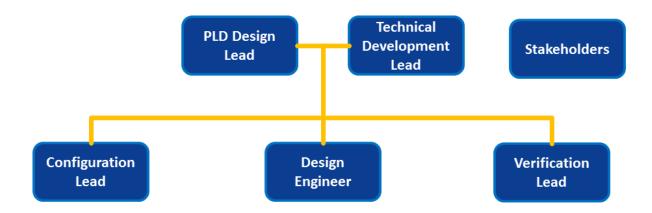

A possible role-based organization chart of the development team is shown in figure 2, Example Development Team Role-Based Organization Chart, follows.

Figure 2—Example Development Team Role-Based Organization Chart

In addition to the development team, the corresponding delivery organization also plays an integral role in the development process. It is the delivery organization's responsibility to:

- a. Ensure the quality of its products through defining and enforcing local design and monitoring processes.

- b. Support the assembling of review boards.

The line organization can delegate this authority to the PLD design lead.

## 5.2 The Development Plan

The PLD design process includes documenting a development plan(s) for the developers to follow. This plan(s) documents the systematic approach used to manage, design, verify, document, and review all PLDs delivered. Development planning involves defining several items that have long-term implications on the project. These can include the following:

- a. Development tools.

- b. Metrics measurement.

- c. Risk management.

- d. System safety considerations

- e. Configuration management.

- f. Training.

- g. Schedule.

- h. Bug tracking.

- i. Project deliverables.

- j. Review planning.

k. Roles and Responsibilities.

The design team can customize the development plan depending on the complexity and project requirements. All items listed above do not necessarily require a separate detailed plan. The team notes each item, the related activities, and issues that affect the cost and schedule. Many times these plans can be a part of an overall project development plan.

## **5.2.1 Development Tools**

The technical development lead determines the development tools and version to be used. This includes at least the following:

- a. Determine a specific list of tools with the following information:

- (1) Manufacturer.

- (2) Tool.

- (3) Version.

- (4) Function.

- (5) Repository for tool archival.

- b. Determine the rationale for tool upgrades. It is a best practice not to upgrade the tools without sufficient justification (e.g., re-characterization of the targeted device and/or a bug fix that would affect the functionality of the programmed PLD). When an issue warrants a tool update, revise the development plan and notify the development team.

- c. Determine how tool alerts, such as Government Industry Data Exchange Program (GIDEPs) or manufacturer notices, will be communicated to the design team. This could come from other discipline areas, such as assurance or parts engineering. This is also applicable to the PLD itself, not only the programming tool.

- d. Determine a data back-up/recovery plan.

#### **5.2.2** Metrics Measurement

Advances in today's technology have allowed PLD capacity to become increasingly dense. Therefore, PLD designs have also become proportionally more complex. There is a need for projects and programs to be able to measure the progression of the PLD design toward the final end product. Metrics measurement allows project management to track PLD design through design, implementation, verification, and integration.

The objectives of the measurement process are as follows:

- a. To provide visibility into the design progress.

- b. To complete the development per the agreed-upon schedule and budget.

- c. To identify programmatic risks.

- d. Monitor accepted and rejected design change requests.

The PLD team lead would be responsible for collecting project metrics, storing them in the project folder, analyzing the measurement data and reporting them periodically. The report may also contain a summary statement of the metrics pointing out any measurements trending towards a limit that may indicate a pending problem. Project metrics for each PLD can include:

- a. Coverage metrics (code and functional).

- b. Design effort (man-hours) planned versus actual.

- c. Budget planned versus actual.

- d. Requirements stability—number of requirements, number of requirements changes, and number of items to be determined (TBDs).

- e. Device resource utilization in percentage of capacity per phase (e.g., C-cells, S-cells, PLD inputs/outputs (I/Os), static random access memory (SRAM) memory, timing, etc.)—actual.

- f. Requirements verification progress (procedures or test benches developed and verified).

- g. Number of problem reports and review item discrepancies—open, closed, and withdrawn.

- h. Number of reviews—planned versus actual.

- i. Risks and mitigations.

#### 5.2.3 Risk Management

Depending on the size and project requirements of the PLD development, the development team will want to identify and manage risks. The technical development lead identifies and manages the risks. Pay special attention to areas such as the following:

- a. Device resource utilization.

- b. Timing.

- c. Power consumption.

- d. External interfaces.

The project's risk management team owns these items; the PLD team does not hold them.

### **5.2.4** System Safety Considerations

Safety-critical applications impose requirements on a project's system safety team to develop key documents, including a safety data package and a hazard report. For such safety-critical PLD designs, the PLD team could be tasked with supporting the safety team to provide information that they can use to document hazards and their mitigation. Hazard identification could cover safety elements:

- a. Controlled by the PLD.

- b. Monitored by the PLD.

- c. Caused by the PLD.

- d. Mitigated by the PLD.

NASA requires Safety and Mission Assurance (SMA) to validate the verification of safety requirements. This can include the witnessing of tests. This validation typically happens at levels higher than the PLD, such as at box or subsystem level. For those cases where validation is applied down at the PLD level, PLD verification planning needs to accommodate key participants such as SMA.

### 5.2.5 Configuration Management and Revision Control

The project or Center defines formal CM for control of released items. At lower levels, the PLD team or line organization typically establishes a revision control system to manage the changes to and archiving of working documents and design files. A controlled item is anything submitted to the revision control or CM system. A typical system needs to incorporate capabilities including the following:

- a. Comprising an established tool or proven process.

- b. Method(s) for identifying/marking a controlled item.

- c. The process for modifying a controlled item.

- d. The process established for user access and privileges.

- e. Institutional IT Security measures necessary to secure controlled items for unauthorized access.

The PLD team follows established processes for revision control. If none exist, then they work with their line organization to establish revision control. The PLD team, in conjunction with the project, if necessary, determines the minimum document and design file types to be controlled. A set of revision-controlled items typically includes the following:

- a. Design environment (e.g. \*.ADB file for MicroSemi devices).

- b. Design and test files.

- c. Deliverables.

At a minimum, any time the design team programs the design into a physical device, it also puts the controlled items into the revision control system. It is best practice to keep all files used in design, simulation, and hardware testing under revision control. This is especially useful in diagnosing problems where the design needs to revert to a prior test configuration.

### **5.2.5.1** Design Environment

The revision control goal for the design environment is to ensure that the design environment is documented, controlled, and reproducible. These revision control items include the following:

- a. Design tools such as those used for simulation, synthesis, PnR, and PLD programming. If the design is not text- or HDL-based, such as Matlab or schematic, keep the design entry tool under revision control.

- b. Setup, project files, and any other file that can dictate the behavior of the design tool.

- c. Script files and makefiles.

## 5.2.5.2 Design and Test Files

All files used in design, simulation and hardware testing are kept under revision control. This set of revision-controlled items typically includes the following:

- a. Design documents (design specifications, the verification plan, test procedures, etc.).

- b. Files needed for producing the design.

- c. Internal or external IP that is used for the design.

- d. Simulation test benches and environment.

- e. Models used in simulation.

- f. Test software and test scripts used during PLD hardware testing.

- g. Information obtained from reviews (e.g., peer reviews, action items, defects found, etc.).

- h. All results from verification efforts including test results. Any known or open issues related to this design.

- i. All programming files (fuse files, bit files, etc.).

- j. Bug reports.

It is a best practice to adopt one of the common software revision control tools (e.g., Concurrent Versions System (CVS) or Subversion (SVN)) to manage the files. In addition to keeping the test software and scripts under revision control, the design team records the script, software, and hardware version information in the test log and archives it along with the test artifacts. The design team reconstructs the test environment when troubleshooting a problem using these items.

#### 5.2.5.3 Deliverables

The development plan also defines how the delivered design is uniquely identified within the version control system. This includes the identifying files used for programming the design, the programmed device, and information about when to use the programmed device in a higher assembly. Section 10 contains a list of delivery items.

### 5.2.6 Training

Training may be required to ensure that all members of the development team maintain a core skill set. The skills can include, but are not limited to:

- a. Digital design (basic design, I/O standard, I/O thresholds, etc.).

- b. Design capture (VHDL, Verilog, etc.).

- c. Design analysis (worst-case analysis, signal integrity analysis, etc.).

- d. Radiation effects.

- e. Design tools (synthesis, PnR, etc.).

- f. Verification (simulation techniques, test techniques, etc.).

- g. CM tools or revision control tools.

The PLD team identifies the needed training and records the costs and schedule to implement it in the development plan. The team also itemizes training costs in the development budget.

#### 5.2.7 Schedule

The PLD team lead creates and maintains the schedule for the PLD life cycle, which includes, but is not limited to:

- a. All the tasks and work products required to implement this plan. Include planning through the verification effort.

- b. All receivables (products that are delivered to the PLD team) that affect the ability to implement the development (e.g., tools, IP cores, development hardware, etc.).

- c. The assigned resource and individual responsible for each task/work product.

- d. All project level reviews (preliminary design review (PDR), critical design review (CDR), code reviews, etc.).

- e. Dependency links with the upper-level project schedule tasks that ensure the development activities occur at the required times.

- f. Upon approval, the schedule is baselined with an initial cost estimate.

- g. Deliverables.

- h. Training.

- i. Monitor progress against schedule periodically.

- j. Identify issues that affect the PLD development team's ability to adhere to the schedule.

- k. Revise schedule as problems are discovered or new requirements added.

#### 5.2.8 Bug Tracking

Bugs are errors in the design or implementation. "Bug tracking" tools simplify the process of capturing and tracking bugs and the exact logic and test case versions required to recreate them. This tool is useful for tracking project-level metrics related to defects found versus defects fixed. It is a best practice for the PLD development team to have a tool for tracking bugs, issues, or potential design changes. Bug tracking information can include:

- a. A description of the error, issue, and/or potential design change.

- b. The PLD version.

- c. The severity of the error, issue and/or potential design change.

- d. The status of the error or issue (open, resolved, in progress, use as is).

- e. The test configuration.

- f. The individual assigned to resolve the error or issue, or to implement the design change.

- g. The required completion date/release date.

- h. A closure statement identifying the resolution and the source version number with the change.

- i. Any impacts to safety.

A best practice for bug tracking is to select a tool that is searchable, sortable, and provides statistics for a number of open, resolved items. For larger projects, this simplifies the gathering of metrics and the sorting of large quantities of issues.

#### **5.2.9 Product Deliverables**

Every PLD delivery includes at least the products itemized in section 10. The PLD team lead identifies the expected deliverable(s) for this unique development. If there are intermediate developmental deliveries, they are identified and documented in the development plan.

All product deliverables are included in the schedule.

## 5.2.10 Review Planning

The development plan defines the appropriate types of reviews that will occur and the appropriate stakeholders that can participate for each review. For purposes of this document, a broad range of possible reviews and participants is provided. The reviews will be customized per the complexity of the design.

The reviews ensure that the design meets all of its requirements for its intended application early in the development process to prevent costly debug and rework. Benefits of reviews include the following:

- a. The identification of issues.

- b. The clarification of requirements.

- c. The sharing of knowledge (technical knowledge, lessons learned, etc.).

- d. The generation and satisfaction of exit criteria prior to proceeding to the next phase.

Reviews listed in table 1, List of Possible Reviews, are internal to the PLD development team and separate from the project milestone reviews. Depending on the project, the schedule of the reviews may be planned to coincide with project-level reviews. The reviews and list of involved participants can be customized based upon the complexity of the design.

**Table 1—List of Possible Reviews**

| Phase                                      | Possible Reviews          | Possible Participants          |  |

|--------------------------------------------|---------------------------|--------------------------------|--|

| Planning and Requirements                  | Planning Document(s)      | Project, Line Management,      |  |

|                                            |                           | Stakeholders, PLD Technical    |  |

|                                            |                           | Development Lead               |  |

|                                            | Requirements Review       | Project, Stakeholders, PLD     |  |

|                                            |                           | Technical Development Lead     |  |

| Preliminary Design                         | Architecture Review       | Stakeholders, PLD Technical    |  |

|                                            |                           | Development Lead, Subject      |  |

|                                            |                           | Matter Experts as appropriate. |  |

|                                            | Preliminary Design Review | Stakeholders, PLD Technical    |  |

|                                            |                           | Development Lead, Subject      |  |

|                                            |                           | Matter Experts as appropriate. |  |

| Detailed Design Design Specification Revie |                           | Stakeholders, PLD Technical    |  |

|                                            |                           | Development Lead, Subject      |  |

|                                            |                           | Matter Experts as appropriate. |  |

|                                            | Detailed Design Review    | Stakeholders, PLD Design Team, |  |

|                                            |                           | Subject Matter Experts as      |  |

|                                            |                           | appropriate.                   |  |

| Implementation                             | Code Review(s)            | PLD Design Team, subject       |  |

|                                            |                           | matter experts                 |  |

|                                            | Synthesis Review          | PLD Design Team, subject       |  |

|                                            |                           | matter experts                 |  |

|                                            | PnR Review                | PLD Design Team, subject       |  |

| Phase              | Possible Reviews        | Possible Participants                   |  |

|--------------------|-------------------------|-----------------------------------------|--|

|                    |                         | matter experts                          |  |

| Verification Phase | Verification Review     | tion Review Stakeholders, PLD Technical |  |

|                    |                         | Development Lead, Verification          |  |

|                    |                         | Lead                                    |  |

| Delivery Review    | Ready to Program Review | Stakeholders, PLD Technical             |  |

|                    |                         | Development Lead, Verification          |  |

|                    |                         | Lead                                    |  |

### 5.2.11 Design Review Checklist

Design review checklists are often used for reviews to facilitate the design review process. Depending on the focus of the review, some review checklists can have more details than others can. Appendix B contains sample checklists.

## 5.3 Requirements

Requirements are allocated to each electronic assembly and flowed down to the board and ultimately the PLD. PLD requirements are negotiated between the board design lead and the technical development lead. The requirements development process iterates as needed. Analyze and review allocated requirements during each iteration. Any issues and questions that are found are discussed and resolved. As a result of this review and discussion, the allocated requirements are refined, clarified, and new requirements derived as needed. For complex PLD designs with many requirements, tracking such requirements can be aided by using a formal requirements database tool such as the Dynamic Object-Oriented Requirements System (DOORS).

#### **5.3.1** Requirements Document

The technical development lead generates a PLD requirements document to capture all the requirements that flowed down. The technical development lead also provides requirements traceability and derived requirements. Once baselined, this document provides traceability for the implementation, and establishes the guidelines for the test and verification steps. Most PLD requirements flow down from the board-level requirements, and can include:

- a. Functions to be implemented from the requirements. Block diagrams are appropriate for upper-level function only.

- b. Performance (speed, critical timing, throughput).

- c. Interface requirements (signal levels, timing, interface-specific data formats).

- d. Environmental constraints (thermal, radiation level at part, mission duration).

- e. Testability requirements (Joint Test Action Group (JTAG), board scan, software, observable internal points).

- f. Redundancy requirements.

- g. IT Security (any security requirements on the fielded device, such as mitigation of reverse engineering or unauthorized access).

- h. Safety-critical requirements.

For safety-critical requirements, a unique identification can be used. The identification will be used by SMA to identify the appropriate level of verification for the requirements that are safety critical.

For smaller projects, the PLD requirements can be documented in the requirements at either the board or box level and identify the PLD requirements as such.

## 5.3.2 Requirements Traceability

A traceability matrix provides for top-down and bottom-up requirements tracing. Top-down tracing, such as change impact analysis, verifies that requirements are implemented, and assesses the impact of a system-level requirement change. Bottom-up tracing, such as defect impact analysis, ensures that only required features are present and assesses the impact on the higher level system of any defect found at a low level.

# **5.3.3** Requirements Maintenance

The technical development lead maintains the requirements document. This includes a process for new or changing requirements that involves the following activities:

- a. Analyze the requirements change to determine schedule and cost impacts.

- b. In the event of a conflict, assemble the appropriate people to work the issue until impacts and resolutions are determined.

- c. Analyze the requirements change for technical impact.

- d. Analyze the requirements change for risk impact, including safety.

See also section 5.2.3 for project risks.

## **5.3.4** Safety Considerations

Safety considerations are typically translated to requirements at the PLD level, such as redundancy, interlocks, upset rates, etc. Appendix E contains additional design considerations. For safety-critical designs, use design criteria 5 found in table 5, PLD Classification, of Appendix C.

#### 5.4 Verification Plan

The verification lead generates the verification plan for verification activities, which includes methods, environments, and criteria. The verification plan documents the plan to verify that the design meets all requirements, is subject to the review of the project team, and includes details regarding how the verification team will record, address, and track to closure the results of verification activities. Verification occurs to the lowest level possible. PLD design verification typically comprises simulations and testing in a hardware environment. Under the formal list of verification methods, simulation falls under analysis.

Independent verification is recommended for larger and more complex projects or safety-critical applications, because it supports a more objective interpretation of the requirements. The advantage here is a more complete assessment of the design.

The verification plan typically includes the following:

- a. Formal methods of verification, from a systems engineering standpoint, typically include:

- (1) Inspection.

- (2) Analysis (e.g., simulation, etc.).

- (3) Demonstration.

- (4) Test (preferred verification method).

- b. Environment of verification (e.g., hardware test configurations; the simulation approach, including test bench descriptions; identification of additional verification, such as negative testing or simulations).

- c. Identify verification method for each requirement. This is necessary for requirements traceability.

- d. Test descriptions, including:

- (1) Test identifier.

- (2) Requirements addressed by the test case.

- (3) Prerequisite conditions.

- (4) Test input.

- (5) Instructions for conducting procedure.

- (6) Expected test results, assumptions, and constraints.

- (7) Criteria for evaluating results.

- (8) Requirements traceability.

- (9) Identification of test configuration.

## **5.4.1** Verification of Intellectual Property Cores

The use of IP cores (acquired, inherited, reused) does not eliminate the need to verify the core. See section 6.3 for more information on the use of IP. Considerations for the verification of IP cores include:

- a. Verify that the designer has reviewed the latest IP core data sheet specifications, application notes, revision notes, test benches, addendums or errata notices for core modifications, updates, license agreement, and any vendor documentation describing the extent of vendor verification of their IP cores.

- b. When using heritage design or design elements, verify that the IP has been demonstrated to meet all requirements in the new intended application.

- c. Verify that the verification (simulation and hardware test) strategy is robust enough to maximize coverage of functional or operational scenarios and configuration (e.g., "test as you fly," "fly as you test").

- d. Verify project requirements on radiation have been implemented in the IP core design. In other words, verify that the IP core can be synthesized to incorporate any necessary radiation-mitigation strategies, such as triple mode redundancy (TMR) or, for the case of a hard core, comes implemented with appropriate radiation-mitigation strategies.

- e. For externally obtained IP, seek vendor-created test bench files/examples for verification.

#### **5.4.2** Tool Verification

The purpose of tool verification is to identify errors that the tool may inject in the design. While it is possible to verify some tools, it is costly. A more effective method to mitigate the risk is through extensive PLD verification using accepted industry-standard tools. It is a best practice for the designer to read all errata that came with the tools and be part of the user community so that errors/workarounds can be mitigated/used early.

#### **5.4.3** Verification Matrix

The verification matrix maintains traceability from the requirements through the verification of all the requirements. The matrix shows how the requirements are described/designed in the design specification and where in the verification plan the requirements are tested. Finally, it traces the requirements into the verification documentation (test procedure, test bench, analysis report, etc.) that identifies how the requirement is verified. Table 2, Sample Verification Matrix, below shows an example.

**Table 2—Sample Verification Matrix**

| Requirement | Design Specification | Verification<br>Method<br>(I,A,D,T) | Verification<br>Plan | Test Procedure/<br>Test Bench/<br>Analysis Report |

|-------------|----------------------|-------------------------------------|----------------------|---------------------------------------------------|

| 1.5.7 abc   | Section 2.3.5        | Т                                   | Section 1.3          | TPR-123                                           |

### 6. PRELIMINARY DESIGN PHASE

During the PDP, the design team generates a top-level design to describe the overall architecture of the design. For small projects, the design team may combine the preliminary design in the DDP. For these projects, the system-level design, the subsystem design, and the assembly design may incorporate the preliminary design.

## 6.1 Entry Criteria

The PDP is the design phase that begins the design cycle. The top-level design is generated in the PDP. With the design of the top level, the items from the planning phase can be updated and changes identified. The PDP can be entered when the following criteria are met:

- a. Development plan is baselined.

- b. PLD requirements are written, but may not be baselined.

This list does not include all elements of the planning phase. It allows for work to proceed while additional planning is in progress.

## **6.2** Design Specification (Preliminary Version)

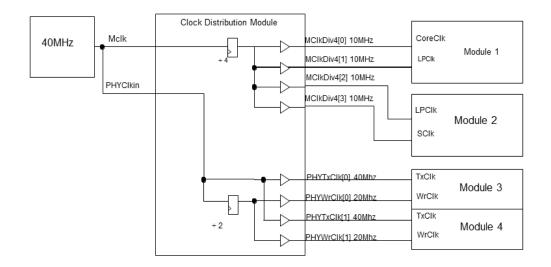

The preliminary version of the design specification is prepared, reviewed, and baselined. The specification can include the following items:

- a. A board-level block diagram depicting PLD internal and external interfaces.

- b. A top-level block diagram of the PLD architecture.

- c. Data flow diagram(s).

- d. Selected PLDs part type(s) with preliminary utilization estimates.

- e. A clock distribution description with frequency information.

- f. A reset distribution description.

- g. Radiation effects mitigations (e.g., scrubbing, TMR, etc.).

- h. Board-level considerations (e.g., signal integrity, power integrity, power consumption, etc.).

- i. A description of all hardware and software interfaces.

- j. Re-configurability requirements (if applicable).

If the PLD interfaces to elements outside the board, then the design team includes a system-level block diagram.

## **6.3** Interface Definition (Preliminary Version)

The interface definition defines the interface between multiple interfaces (e.g., multiple pieces of hardware, hardware and software, avionics and software, etc.). This document need not be unique to the PLD. It can be part of a larger document.

The preliminary version of the interface specification is prepared, reviewed, and baselined. The interface specification can include the following items:

- a. The register interface.

- b. Bit definitions of registers.

- c. All interface signals.

- d. Memory map.

- e. Protocols (e.g., RS-422, PCI, 1553, etc.).

- f. Pinout.

# **6.4** Use of Intellectual Property (In-House or Out-of-House)

Each development organization documents the approach to meeting certification requirements for any computing system's hardware elements that include any off-the-shelf (OTS) components (e.g., a previously designed "heritage" circuit board assembly, an application-specific integrated circuit (ASIC) used in another design, IP procured or obtained from another source.)

Each developer of PLDs that include non-development items (i.e., design elements that are reused from another application or that are procured or obtained from a source outside their developmental control, such as IP) ensures that the inclusion of such non-development items meets all the requirements of the PLD design in its intended application. This assessment extends to the overall circuit design as well.

When purchasing IP, the licensing agreements are reviewed to make sure they extend through the life of the project. This includes the maintenance phase. Additionally, purchased IP may not

include the source code or the detailed core design, possibly making testing of the core very difficult. When the source code is not available, the project has to analyze the risk of using that core. The core will have to be verified without the ability to review the source code completely. There may also be limited access to testing the core. The project team weighs the risk versus the benefits of that core.

When purchasing IP, allow your Center's legal team to review the licensing agreement. Licensing agreement negotiations can be lengthy, impacting the schedule. Also, ensure that the agreement extends through the life of the project, including the maintenance phase.

#### 6.5 Exit Criteria

The PDP is the first phase of the design cycle. The PDP is complete when the following criteria have been met:

- a. The preliminary design is complete.

- b. A preliminary version of the design specification is baselined.

- c. The interface definition(s) are baselined.

- d. A list of proposed IP (heritage and new) that will be used in the design is identified.

- e. Reviews are completed as defined in the development plan.

- f. The planning phase documents (see section 5) are baselined, including:

- (1) Requirements.

- (2) Development plan.

- (3) Verification plan.

### 7. DETAILED DESIGN PHASE

The DDP is entered upon completion of the PDP. The DDP generates the design specification, but not the design files used to implement the PLD. Detailed design information, such as timing diagrams, detailed block diagrams, is developed during this design phase. The information developed in this phase is used for capturing the design during the design implementation phase.

### 7.1 Entry Criteria

The DDP details the PLD design information as well as generating the complete design. The DDP can be entered when the following criteria are met:

- a. The preliminary design specification is baselined.

- b. The interface definition is baselined.

- c. The PDP and associated reviews are successfully completed.

- d. The planning phase documents (see section 5) are baselined, including:

- (1) Requirements.

- (2) Development plan.

- (3) Verification plan.

# 7.2 Coding Standard

It is recommended that the PLD team utilize a common HDL coding style. Design organizations may consider the use of common coding standards across multiple projects, in order to facilitate effective reviews and design insight.

The following items help make a design reviewable:

- a. Standard coding style.

- b. Documentation that is consistent with the design.

- c. Current, regularly updated documents.

- d. Use of appropriate comments for the design.

- e. Use of configuration control for the design.

Examples of the types of HDL standards that may be defined include, but are not limited to:

- a. Use of naming conventions to allow recognition of the function of signals by their name.

- b. Use of the header of the HDL design to capture nomenclature (see Appendix A).

- c. Use of modular design to ease testability, readability, and simulation.

- d. Use of editor tools (tool editor software, Ultra-Edit, use of spaces versus tabs, etc.).

- e. Use of self-checking/documenting test-benches.

- f. Use of proper code documentation, particularly inline documentation, which later helps if a personnel change is made in the middle of the project.

- g. Documentation of each procedure or function.

- h. Use of inline comments to explain thoroughly the applicability of assumptions and rationale used to achieve the design.

- i. Use of a consistent design language across all designs, agreed upon at the project/branch level.

## 7.3 Design Standard/Best Practices

This section describes a list of items that are design specific. The PLD designer reviews all the items to decide which are applicable and which are not.

## 7.3.1 Synchronous Design

It is recommended as a best design practice to use synchronous design methods. The behavior of a synchronous design is predictable/deterministic and more tolerant to race conditions, hazards (dynamic or static), or glitches introduced by environmental conditions. Fully synchronous designs can also be more easily migrated or reused across PLD device types. The use of non-synchronous design methods is rarely appropriate, and their use has to be sufficiently justified, because they usually require more effort to validate or verify in the design.

Synchronous design techniques include the following:

- a. Transition all signals on the clock edge.

- b. Avoid using a gated clock (a clock that is driven from logic, not a clock buffer).

- c. Handle carefully signals that cross clock domains. There are many techniques, such as double registers; metastable resistant registers; first in, first outs (FIFOs); etc. The design identifies the best method for the particular implementation.

- d. Synchronize asynchronous inputs to system clock in one location.

- e. Minimize the number of clock domains.

- f. Utilize synchronously de-asserted rests.

## 7.3.2 Clock Design

When following synchronous design methodology, a PLD best practice is to use low-skew clock buffers on clock and reset nets. Use of low-skew clock buffers simplifies timing analysis and avoids race conditions (e.g., hold-time violations) by enabling more simultaneous (synchronized) clock arrival times. This ensures more deterministic functional behavior. Therefore, when sequentially adjacent registers are clocked on a common edge, use low-skew clock resources. It is acceptable to design with routed clocks, and this can often result in a reduction of power consumption or an effective increase in the number of clocks available. However, precise skew-tolerant design techniques and analysis have to be used. In addition, routing clock signals over long distances inside the PLD to the inputs of clock buffers using regular routing resources may make the signals vulnerable to crosstalk from nearby signals, possibly resulting in errant behavior. To avoid this, ensure that PLD clock input pin or logic that generates the clock is close to clock buffer input.

#### 7.3.2.1 Chip-to-Chip Timing Strategy

Many analysis tools are useful for analyzing logic within a single chip, but few are effective at analyzing system or chip-to-chip timing. In addition, while the worst-case behavior of the clock-to-out of the source chip is easily analyzed using "minimum" or "best case" timing parameters, the hold time of the destination chip may need to be analyzed assuming a slow path for the clock and a fast path for the data for the same calculation. A strategy to consider would be to assign or allocate delays to each signal leaving one device and being received at the next. These

allocations can be used as constraints for synthesis and timing analysis to ensure that the system will meet timing once integrated.

In general, rigorous analysis of the chip-to-chip interface delays and clock skew is performed to validate the destination capture scheme. Analysis considerations include the following:

- a. Trace delays from board-level connections (or other medium connectors).

- b. Output (source chip) and input (destination chip) buffer delays.

- c. Delays from input buffer routing to internal structures.

- d. Clock tree latency.

- e. Signal skew.

- f. I/O signal integrity (e.g., transmission line effects, ground bounce, and cross talk).

The optimum criteria for passing is that all worst-case setup and hold times are always satisfied.

### 7.3.2.2 Delay-Locked Loops (DLLs) and Phase-Locked Loops (PLLs)

Consider the analysis required before using the DLLs and PLLs. DLLs and PLLs can have many useful functions in digital systems, but they have some requirements that have to be satisfied:

- a. Check that the worst-case frequencies (both slowest and fastest) are compatible with the circuits; often the acceptable ranges are very limited.

- b. When these circuits clock finite state machines (FSMs) or other sequential logic, verify that the DLL/PLL starts up, stabilizes, and locks up properly and reliably to ensure safe circuit operation.

- c. Check the worst-case performance when the DLL or PLL encounters a single event upset (SEU). This can result in a change of programming of the DLL or PLL, which is sometimes subtle, or a change in mode.

- (1) Safe operation of the system has to be ensured during these off-nominal conditions.

- (2) An SEU or single event transient (SET) can cause the DLL or PLL to unlock or glitch and, consequently, make the entire circuit that is within the clock tree unstable or inoperable, necessitating a reset.

- d. Account of DLL/PLL clock jitter and stability.

- e. Power supply and decoupling strategies on the circuit board for the DLL/PLL circuit.

Use of internal DLL/PLL PLD circuitry has to include careful analysis of a project's radiation requirements and available radiation test data on the PLD's DLL/PLL circuitry, which is typically softer than the other elements within the PLD.

### 7.3.2.3 Crossing Clock Domains

FPGA designs with multiple clock domains are now common. Perform clock domain crossing (CDC) analysis. Based on analysis of the clock trees, identify all signals crossing clock domains and determine the need for metastable state resolution. When de-metastability logic is used, it needs to be evaluated for its correctness and effectiveness. This is especially important for reset signals used in each clock domain to ensure proper operation for all possible sequences of reset removal between clock domains. Additionally, ensure that the latency involved in signal synchronization is tolerable to the system.

### 7.3.2.4 Opposite-Edge Clocking

Consider duty cycle in timing analysis for designs that use both clock edges. With justification, document any designs that pass data from one edge of a clock to the other. Analyze such circuits using the worst-case duty cycle for each phase. Often designers assume a 50 percent duty cycle, which may not be the case. Sources of duty cycle distortion include oscillator characteristics, with 50 +/- 10 percent duty cycles being common, including uneven delays through logic gates and buffers, etc. Unless required to meet timing, avoid using opposite-edge clocking as it complicates the timing analysis for the design.

### 7.3.2.5 Metastability

Ensure that proper synchronizers are used for each asynchronous signal to guard against metastability. Often designers will use two series D-flip-flops (DFFs). While this is a common and acceptable topology, be aware that for high-speed signals, the failure rate of this synchronizer can be non-negligible. Analysis has to be done for situations that may require a third DFF to be put in the series. The following are notable conditions to address:

- a. The metastability analysis includes nominal through extreme temperature and voltage values.

- b. Ensure that there is margin in these circuits as they are impractical to test and verify.

- c. Also, note that for ASICs, different flip-flop macros may have significantly different metastable parameters. This can also be a consideration in PLDs.

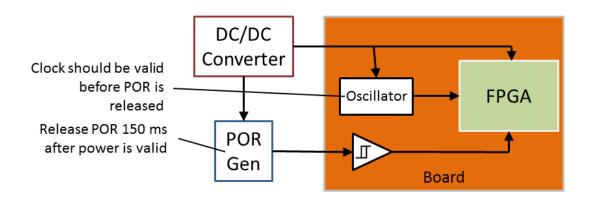

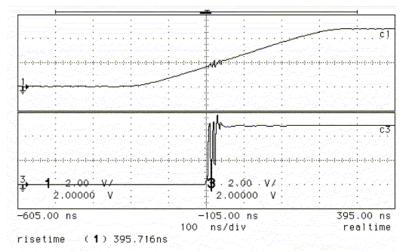

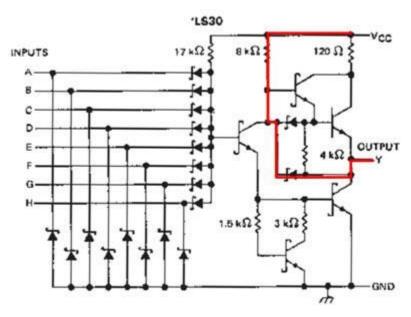

### **7.3.2.6** Latches